Cadence Sigrity 2019是一款专业的高速电路设计仿真软件,这款软件可以将PCB设计和分析扩展到封装和电路板之外。软件基于Sigrity专利技术,可以有效地提升各类高级物理设计的效率。新版本的Sigrity 2019还带来了全新的功能,优化了工作效率。

主要特色:

• 可以分析板上任意结构的电磁耦合特性,为器件/去耦电容的放置位置以及过孔的排布提供依据

• 可以提取IC封装电源网络与信号网络的阻抗(Z)参数及散射(S)参数,研究电源的谐振频率以及输入阻抗,或研究信号的插入损耗及反射系数,为精确分析电源和信号的性能提供依据; 为时域SSN仿真提供可靠的宽带网络参数模型

• 分析整板远场和近场的EMI/EMC性能,全三维显示复杂的近场辐射水平,为解决板级的EMI/EMC问题提供依据

• 分析板上任意位置的谐振特性,找出系统在实际工作时电源平面上的谐振及波动特性,为电源的覆铜方式及去耦电容的放置位置提供依据

• 支持叠层以及其他物理设计参数的假定(What-if)分析,快速评估设计参数对系统性能的影响

• 基于专利算法的精确直流求解引擎(PowerDC),可支持从直流(DC)到宽频段的精确模型提取

• 与三维(3D)IC封装设计和板级设计工具无缝集成

仿真实例:

高速信号在传输的过程中由于layout走线的不良会导致反射串扰等信号完整性问题,这节我们仿真DDR信号特征阻抗和串扰参数,加深对layout的理解。

阻抗不匹配导致的反射失真

串扰

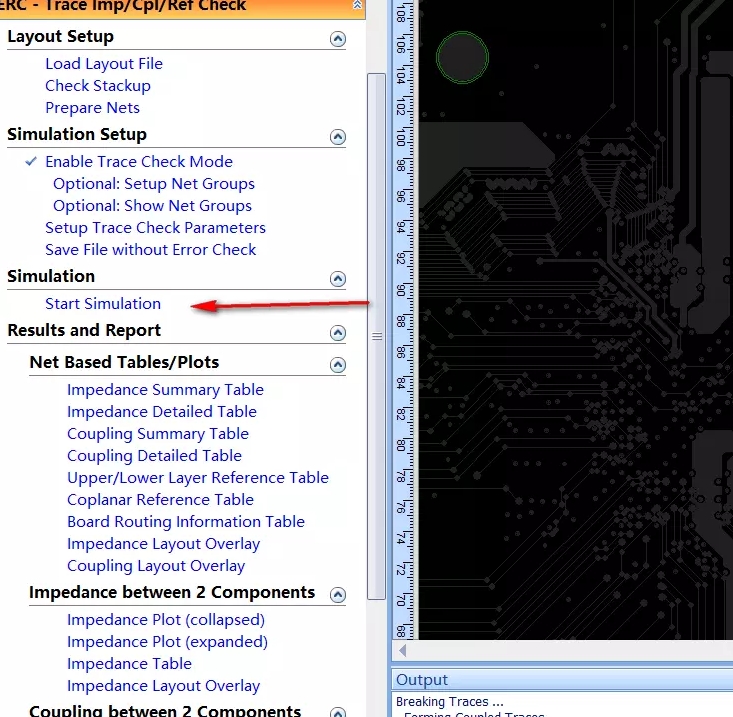

1. 打开PowerSI,load layout file。(我这图是已经仿真完了的)

2. 点击“Setup Net Groups”,选择TX 器件,这里勾选这个线路的CPU U12,点击下一步。

3. 选择RX端,这里勾选这个线路的DDR颗粒U11,点击下一步。

4. 确认电源网络/GND网络,直接点击下一步到分组界面,因为只是练习,我们把DDR的地址和数据等信号都分为一个组,真正项目需要分清楚;点击第一个,再shift点击最后一个,全分为一个组,命名为DDR,然后直接到finish。

5. 点击“Setup Trace Check Parameters”设置检查参数,默认是勾选阻抗和耦合,设置显示耦合2%以上,选择“根据group检查”,点击OK,开始仿真。

6. 仿真结果又表格形式和layout形式,我们偏向于看layout形式,需要具体点时可以再看表格。

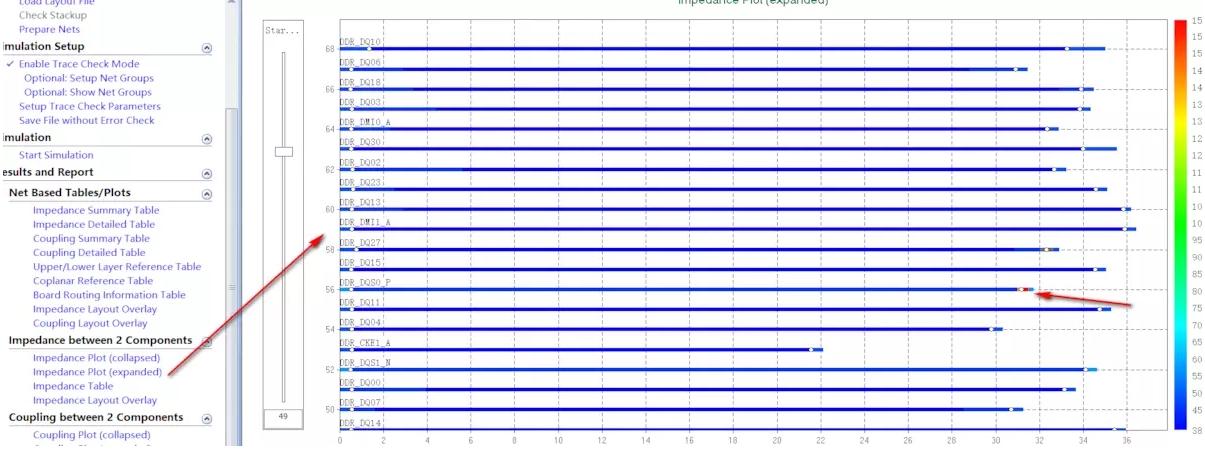

7. impedance layout overlay会将CPU和DDR的走线以layout的形式显示出来,根据颜色区分。

阻抗柱状图也比较直观,每条线摘出来,这里不仅可以看到哪个地方阻抗偏高偏低,还可以看到走线长度。

8. coupling layout overlay通过颜色深浅将串扰强度表现出来,可以看出走线越近的地方串扰越大,一般低于5%信号质量不会受到太大影响。

大小: 331M

大小: 331M Overture专业打谱软件5.5.1-7 简体中文版

Overture专业打谱软件5.5.1-7 简体中文版  SPSS 18.0中文版

SPSS 18.0中文版  剪.映windows电脑版2025官方最新版v7.1.0最新专业版

剪.映windows电脑版2025官方最新版v7.1.0最新专业版  MatLab R2012b 特别文件

MatLab R2012b 特别文件  寻星计算程序(卫星天线寻星参数计算)v3.1 绿色版

寻星计算程序(卫星天线寻星参数计算)v3.1 绿色版  八爪鱼采集器v8.58 官方最新版

八爪鱼采集器v8.58 官方最新版  星空抽奖软件无限制版完美注册码版

星空抽奖软件无限制版完美注册码版  利信财务软件专业单机版V6.4免费无限制版

利信财务软件专业单机版V6.4免费无限制版  天学网电脑版v5.6.1.0 官方最新版

天学网电脑版v5.6.1.0 官方最新版  摩客mockplus桌面客户端v3.7.1.0 官方最新版

摩客mockplus桌面客户端v3.7.1.0 官方最新版  淘宝助理天猫版5.3.7.0 官方最新版

淘宝助理天猫版5.3.7.0 官方最新版  高品智CRM客户关系管理系统v3.301.311 官方免费版

高品智CRM客户关系管理系统v3.301.311 官方免费版  易航科技增值税发票电子化软件(增值税发票扫描认证)V2.0免费版

易航科技增值税发票电子化软件(增值税发票扫描认证)V2.0免费版  易房大师v3.2免费版

易房大师v3.2免费版  杰奇小说连载系统免费版

杰奇小说连载系统免费版  发票导出接口软件3.9绿色免费版

发票导出接口软件3.9绿色免费版  发票认证接口软件v2.2绿色版

发票认证接口软件v2.2绿色版  高品智财务公司委托代办项目软件v3.320 官方版

高品智财务公司委托代办项目软件v3.320 官方版  食草族管理专家V2.5.9 绿色免费版

食草族管理专家V2.5.9 绿色免费版