TTL��CMOS��ƽ

1��TTL��ƽ(ʲô��TTL��ƽ)��

����ߵ�ƽ>2.4V,����͵�ƽ<0.4V���������£�һ������ߵ�ƽ��3.5V������͵�ƽ��0.2V����С����ߵ�ƽ�͵͵�ƽ������ߵ�ƽ>=2.0V������͵�ƽ<=0.8V������������0.4V��

2��CMOS��ƽ��

1����ƽ��ѹ�ӽ��ڵ�Դ��ѹ��0����ƽ�ӽ���0V�����Ҿ��кܿ����������ޡ�

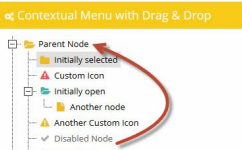

3����ƽת����·��

��ΪTTL��COMS�ĸߵ͵�ƽ��ֵ��һ����ttl 5v<����>cmos 3.3v�������Ի�������ʱ��Ҫ��ƽ��ת������������������Ե�ƽ��ѹ��û��ʲô����Ķ�����

4��OC�ţ������缫��·�ŵ�·��OD�ţ���©����·�ŵ�·�����������������͵�Դ���ܽ����ص�ƽ��Ϊ�ߵ͵�ƽ�á�������һ��ֻ��Ϊ���ش��ѹ�ʹ�������أ������ֽ��������ŵ�·��

5��TTL��COMS��·�Ƚϣ�

1��TTL��·�ǵ���������������CMOS��·�ǵ�ѹ����������

2��TTL��·���ٶȿ죬�����ӳ�ʱ���(5-10ns)�����ǹ��Ĵ�COMS��·���ٶ����������ӳ�ʱ�䳤(25-50ns),�����ĵ͡�COMS��·�����Ĺ����������źŵ�����Ƶ���йأ�Ƶ��Խ�ߣ�оƬ��Խ�ȣ�������������

3��COMS��·������ЧӦ��

COMS��·��������̫��ĵ������ڲ��ĵ��������������жϵ�Դ������һֱ����������ЧӦ��������ЧӦ������������ЧӦʱ��COMS���ڲ������ܴﵽ40mA���ϣ��������ջ�оƬ��

������ʩ�� 1��������˺�����˼�ǯλ��·��ʹ���������������������涨��ѹ��

2��оƬ�ĵ�Դ����˼�ȥ���·����ֹVDD�˳���˲��ĸ�ѹ��

3����VDD�����Դ֮����������裬��ʹ�д�ĵ���Ҳ��������ȥ��

4����ϵͳ�ɼ�����Դ�ֱ�ʱ������Ҫ������˳����ʱ���ȿ���COMS·�õ� Դ���ٿ��������źź��صĵ�Դ���ر�ʱ���ȹر������źź��صĵ�Դ���ٹر�COMS��·�ĵ�Դ��

6��COMS��·��ʹ��ע������

1��COMS��·ʱ��ѹ�������������������ܿ��ܴԸ����źŵIJ�������ǿ�����ԣ����õĹܽŲ�Ҫ���գ�Ҫ��������������������裬����һ���㶨�ĵ�ƽ��

2������˽ӵ�������ź�Դʱ��Ҫ������˺��ź�Դ֮��Ҫ�����������裬ʹ����ĵ���������1mA֮�ڡ�

3�����ӳ��źŴ�����ʱ����COMS��·�˽�ƥ����衣

4��������˽Ӵ����ʱ��Ӧ��������˺͵��ݼ�ӱ������衣����ֵΪR=V0/1mA.V0���������ϵĵ�ѹ��

5��COMS�������������1mA�����п����ջ�COMS��

7��TTL�ŵ�·������˸������ԣ�����˴�������������Ĵ�������

1������ʱ�൱������˽Ӹߵ�ƽ����Ϊ��ʱ���Կ���������˽�һ�������ĵ��衣

2�����ŵ�·����˴���10K�����������͵�ƽ������˳����ֵ��Ǹߵ�ƽ�����ǵ͵�ƽ����Ϊ��TTL�ŵ�·������˸������Կ�֪��ֻ��������˽ӵĴ�������С��910ŷ ʱ�����������ĵ͵�ƽ�źŲ��ܱ��ŵ�·ʶ����������������ٴ�Ļ�����˾�һֱ���ָߵ�ƽ�����һ��Ҫע�⡣COMS�ŵ�·�Ͳ��ÿ�����Щ�ˡ�

8��TTL��·�м��缫��·OC�ţ�MOS��Ҳ�кͼ��缫��Ӧ��©����·��OD�ţ���������ͽ�����©�����OC���ڽ�ֹʱ��©����������Ǿ���©������Ϊʲô��©�����أ�������Ϊ�������ܽ�ֹ��ʱ�����Ļ�������Լ����0�����Dz�����������Ϊ0�����������ܵļ��缫�ĵ���Ҳ�Ͳ��������� 0������Լ0�����������©������

��©�����OC�ŵ�������ǿ�©�����OD�ŵ����Ҳ�ǿ�©��������������պܴ�ĵ��������Dz�����������ĵ��������ԣ�Ϊ��������������������ʹ�õ�ʱ��Ҫ����Դ����������һ���á�OD��һ����Ϊ�������/����������ƽת�����Լ��������մ��ص�������Ҫ��

9��ʲô����ͼ���������뿪©��·��ʲô����

TTL���ɵ�·�У�����н����������ܵ��������ͼ���������û�еĽ���OC�š���ΪTTL����һ�������أ�ͼ����Ҳ�����������������������������������ͼ�ڡ�һ��ͼ��ʽ������ߵ�ƽ400UA���͵�ƽ8MA

+++++++++++++++++++++++++++++++++++++++++++

CMOS �������õ�����˱��������ߵ�ƽ��͵�ƽ, ������Ϊ CMOS �Ǹ������迹����, ����״̬��û�����������. ������õ�������������, ������Ӧ�������ź�, Ӱ��оƬ��������, ����������������ԵĻ�����������, ���оƬʧЧ.

����, ֻ�� 4000 ϵ�е� CMOS �������Թ�����15����Դ��, 74HC, 74HCT �ȶ�ֻ�ܹ����� 5����Դ��, �����Ѿ��й����� 3���� 2.5����Դ�µ� CMOS ����·оƬ��.

CMOS��ƽ��TTL��ƽ:

CMOS����ƽ��Χ�Ƚϴ�Χ��3��15V������4000ϵ�е�5V����ʱ�������4.6����Ϊ�ߵ�ƽ�������0.05V����Ϊ�͵�ƽ��������3.5V����Ϊ�ߵ�ƽ��������1.5V����Ϊ�͵�ƽ��

������TTLоƬ�����緶Χ��0��5V����������5V����74ϵ��5V���磬�����2.7V����Ϊ�ߵ�ƽ������� 0.5V����Ϊ�͵�ƽ��������2V����Ϊ�ߵ�ƽ����0.8V����Ϊ�͵�ƽ����ˣ�CMOS��·�� TTL��·����һ����ƽת�������⣬ʹ���ߵ�ƽ��ֵ��ƥ�䡣

�й�����ƽ��һЩ���� ��

Ҫ�˽�����ƽ�����ݣ�����Ҫ֪�����¼�������ĺ��壺

1������ߵ�ƽ��Vih������֤���ŵ�����Ϊ�ߵ�ƽʱ����������С����ߵ�ƽ���������ƽ����Vihʱ������Ϊ�����ƽΪ�ߵ�ƽ��

2������͵�ƽ��Vil������֤���ŵ�����Ϊ�͵�ƽʱ���������������͵�ƽ���������ƽ����Vilʱ������Ϊ�����ƽΪ�͵�ƽ��

3������ߵ�ƽ��Voh������֤���ŵ����Ϊ�ߵ�ƽʱ�������ƽ����Сֵ�����ŵ����Ϊ�ߵ�ƽʱ�ĵ�ƽֵ��������ڴ�Voh��

4������͵�ƽ��Vol������֤���ŵ����Ϊ�͵�ƽʱ�������ƽ�����ֵ�����ŵ����Ϊ�͵�ƽʱ�ĵ�ƽֵ������С�ڴ�Vol��

5�� ��ֵ��ƽ(Vt)�����ֵ�·оƬ������һ����ֵ��ƽ�����ǵ�·�ո���ǿ�ܷ�ת����ʱ�ĵ�ƽ������һ������Vil��Vih֮��ĵ�ѹֵ������CMOS��·����ֵ��ƽ���������Ƕ���֮һ�ĵ�Դ��ѹֵ����Ҫ��֤�ȶ����� ���������Ҫ������ߵ�ƽ> Vih������͵�ƽ<Vil������������ƽ����ֵ���£�Ҳ����Vil��Vih�������·������ᴦ�ڲ��ȶ�״̬��

����һ�������ƽ�����ϲ����Ĺ�ϵ���£�

Voh > Vih > Vt > Vil > Vol

6��Ioh���������Ϊ�ߵ�ƽʱ�ĸ��ص�����Ϊ����������

7��Iol���������Ϊ�͵�ƽʱ�ĸ��ص�����Ϊ���������

8��Iih����������Ϊ�ߵ�ƽʱ�ĵ�����Ϊ���������

9��Iil����������Ϊ�͵�ƽʱ�ĵ�����Ϊ����������

�ŵ�·������ڼ��ɵ�Ԫ�ڲ��Ӹ��ص����ֱ��������Ϊ����ˣ�������ʽ���ų�Ϊ��·�š���·��TTL��CMOS��ECL�ŷֱ��Ϊ���缫��·��OC����©����·��OD�������伫��·��OE����ʹ��ʱӦ����Ƿ���������裨OC��OD�ţ����������裨OE�ţ����Լ�������ֵ�Ƿ���ʡ����ڼ��缫��·��OC���ţ�������������ֵRLӦ��������������

��1����RL < ��VCC��Voh��/��n*Ioh��m*Iih��

��2����RL > ��VCC��Vol��/��Iol��m*Iil��

����n������Ŀ�·������m�������������������

10�����õ�����ƽ

������ƽ����TTL��CMOS��LVTTL��ECL��PECL��GTL��RS232��RS422��LVDS�ȡ�

������TTL��CMOS������ƽ�����͵�ѹ�ɷ�Ϊ���ࣺ5Vϵ�У�5V TTL��5V CMOS����3.3Vϵ�У�2.5Vϵ�к�1.8Vϵ�С�

��5V TTL��5V CMOS����ƽ��ͨ�õ�����ƽ��

��3.3V�����µ�����ƽ����Ϊ�͵�ѹ����ƽ�����õ�ΪLVTTL��ƽ��

���͵�ѹ������ƽ����2.5V��1.8V���֡�

��ECL/PECL��LVDS�Dz�����������

��RS-422/485��RS-232�Ǵ��ڵĽӿڱ���RS-422/485�Dz�����������RS-232�ǵ������������

++++++++++++++++++++++++++++

���ĵ���

- ��1ҳ: ��ҳ

- ��2ҳ: TTL��CMOS��ƽ

- ��3ҳ: Ϊʲô����OC�ţ�

- ��4ҳ: ʲô��OC��OD��

ϲ��

ϲ��  ��

�� �ѹ�

�ѹ� ��

�� ��

�� ����

����